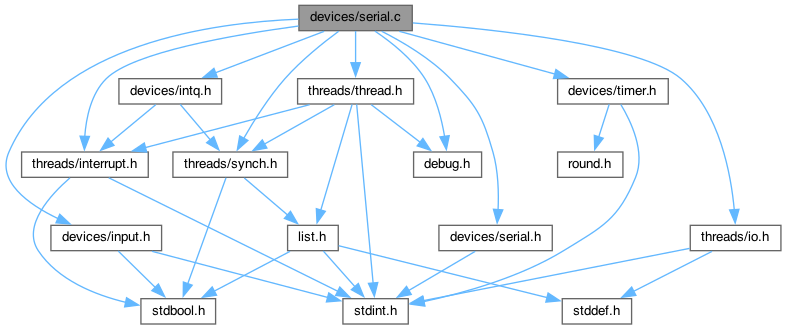

#include "devices/serial.h"#include <debug.h>#include "devices/input.h"#include "devices/intq.h"#include "devices/timer.h"#include "threads/io.h"#include "threads/interrupt.h"#include "threads/synch.h"#include "threads/thread.h"

Macros | |

| #define | IO_BASE 0x3f8 |

| #define | RBR_REG (IO_BASE + 0) /* Receiver Buffer Reg. (read-only). */ |

| #define | THR_REG (IO_BASE + 0) /* Transmitter Holding Reg. (write-only). */ |

| #define | IER_REG (IO_BASE + 1) /* Interrupt Enable Reg.. */ |

| #define | LS_REG (IO_BASE + 0) /* Divisor Latch (LSB). */ |

| #define | MS_REG (IO_BASE + 1) /* Divisor Latch (MSB). */ |

| #define | IIR_REG (IO_BASE + 2) /* Interrupt Identification Reg. (read-only) */ |

| #define | FCR_REG (IO_BASE + 2) /* FIFO Control Reg. (write-only). */ |

| #define | LCR_REG (IO_BASE + 3) /* Line Control Register. */ |

| #define | MCR_REG (IO_BASE + 4) /* MODEM Control Register. */ |

| #define | LSR_REG (IO_BASE + 5) /* Line Status Register (read-only). */ |

| #define | IER_RECV 0x01 /* Interrupt when data received. */ |

| #define | IER_XMIT 0x02 /* Interrupt when transmit finishes. */ |

| #define | LCR_N81 0x03 /* No parity, 8 data bits, 1 stop bit. */ |

| #define | LCR_DLAB 0x80 /* Divisor Latch Access Bit (DLAB). */ |

| #define | MCR_OUT2 0x08 /* Output line 2. */ |

| #define | LSR_DR 0x01 /* Data Ready: received data byte is in RBR. */ |

| #define | LSR_THRE 0x20 /* THR Empty. */ |

Enumerations | |

| enum | { UNINIT , POLL , QUEUE } |

Functions | |

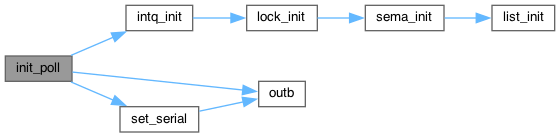

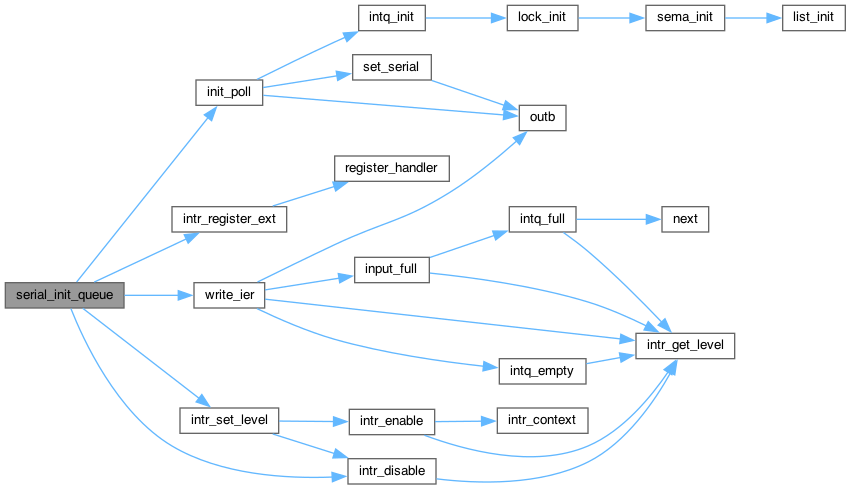

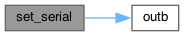

| static void | set_serial (int bps) |

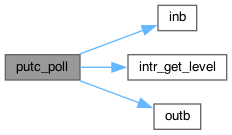

| static void | putc_poll (uint8_t) |

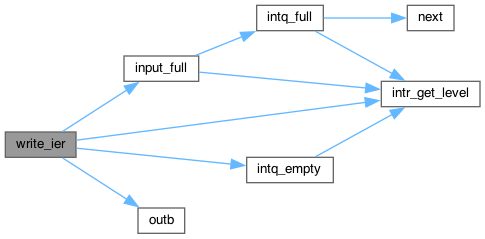

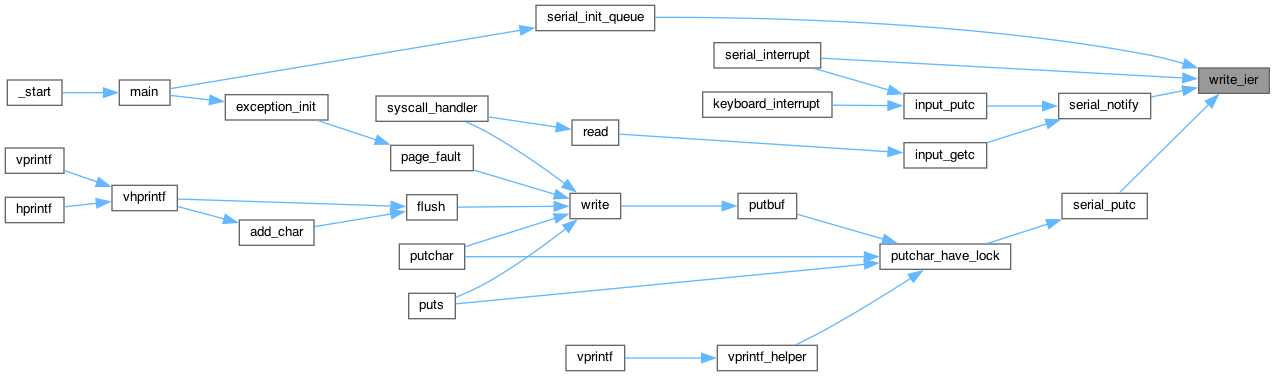

| static void | write_ier (void) |

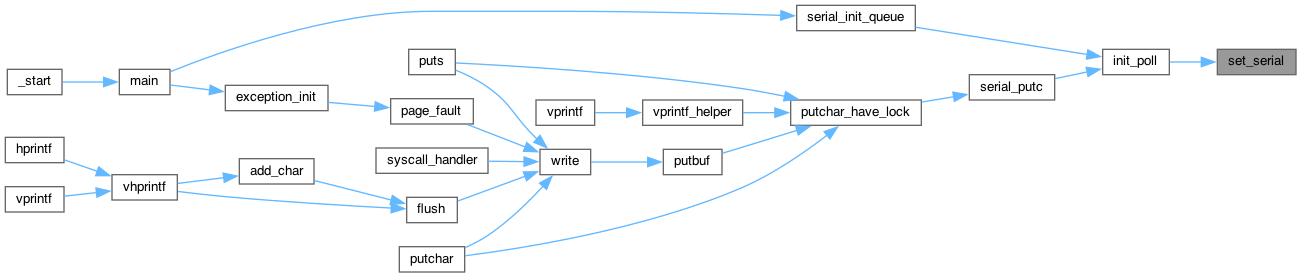

| static void | init_poll (void) |

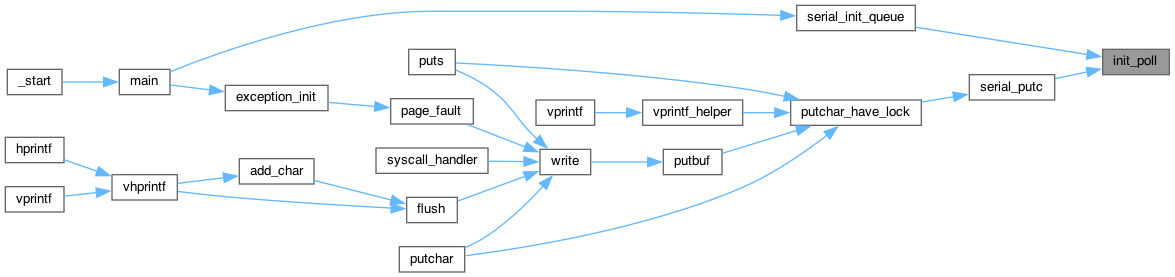

| void | serial_init_queue (void) |

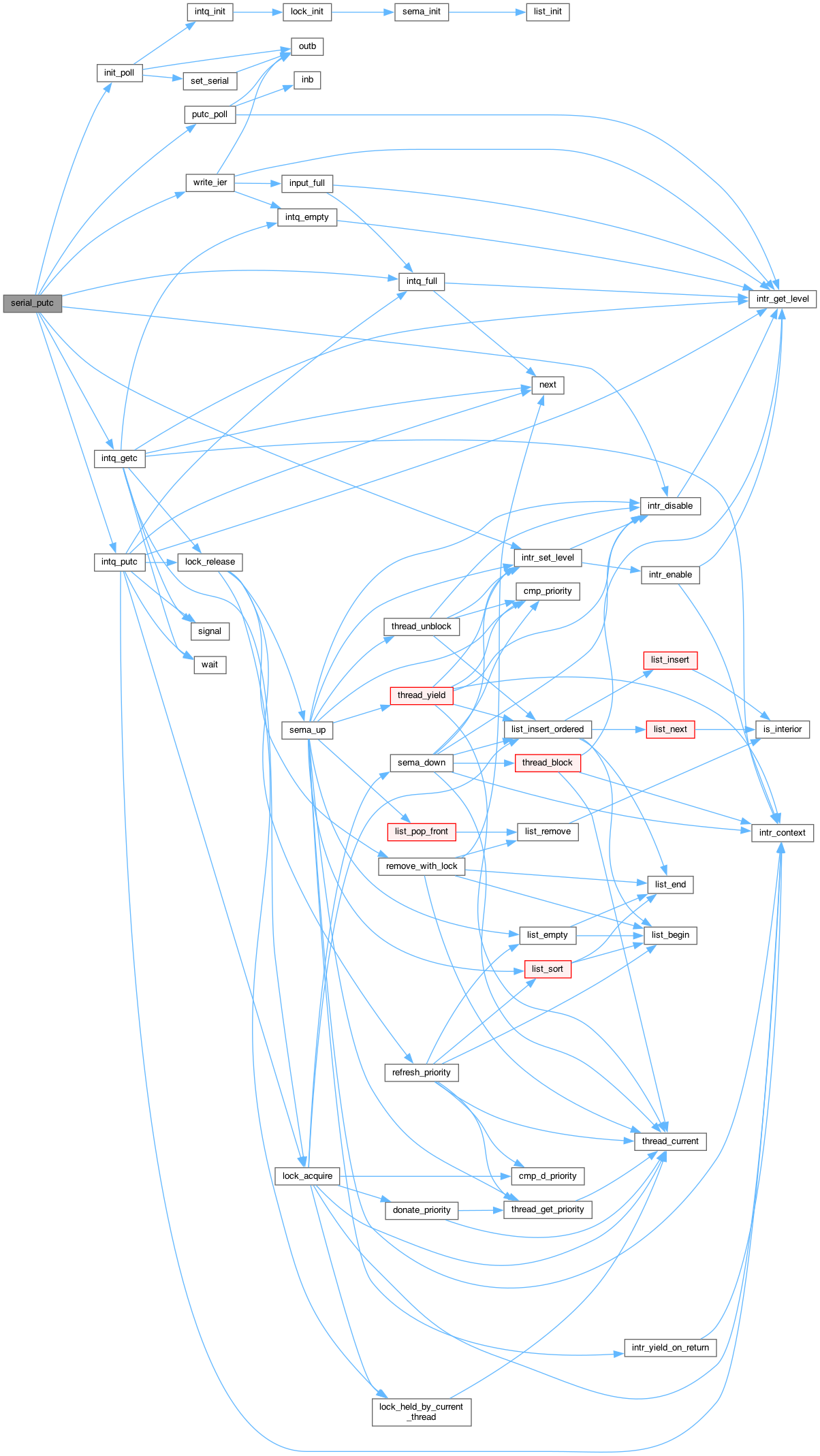

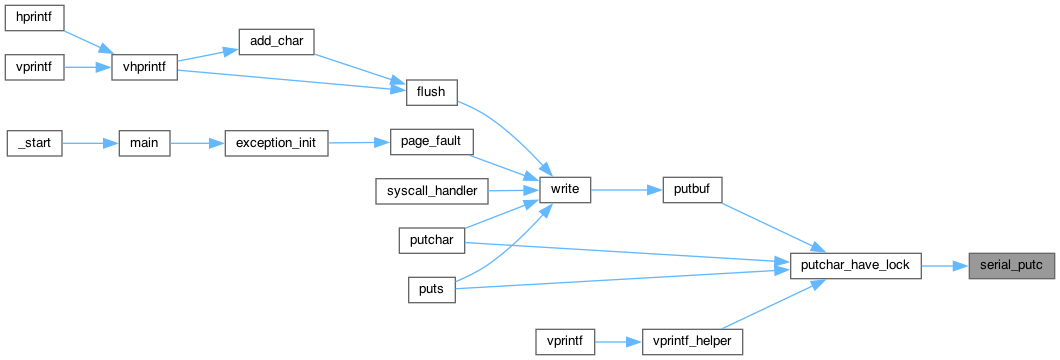

| void | serial_putc (uint8_t byte) |

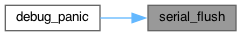

| void | serial_flush (void) |

| void | serial_notify (void) |

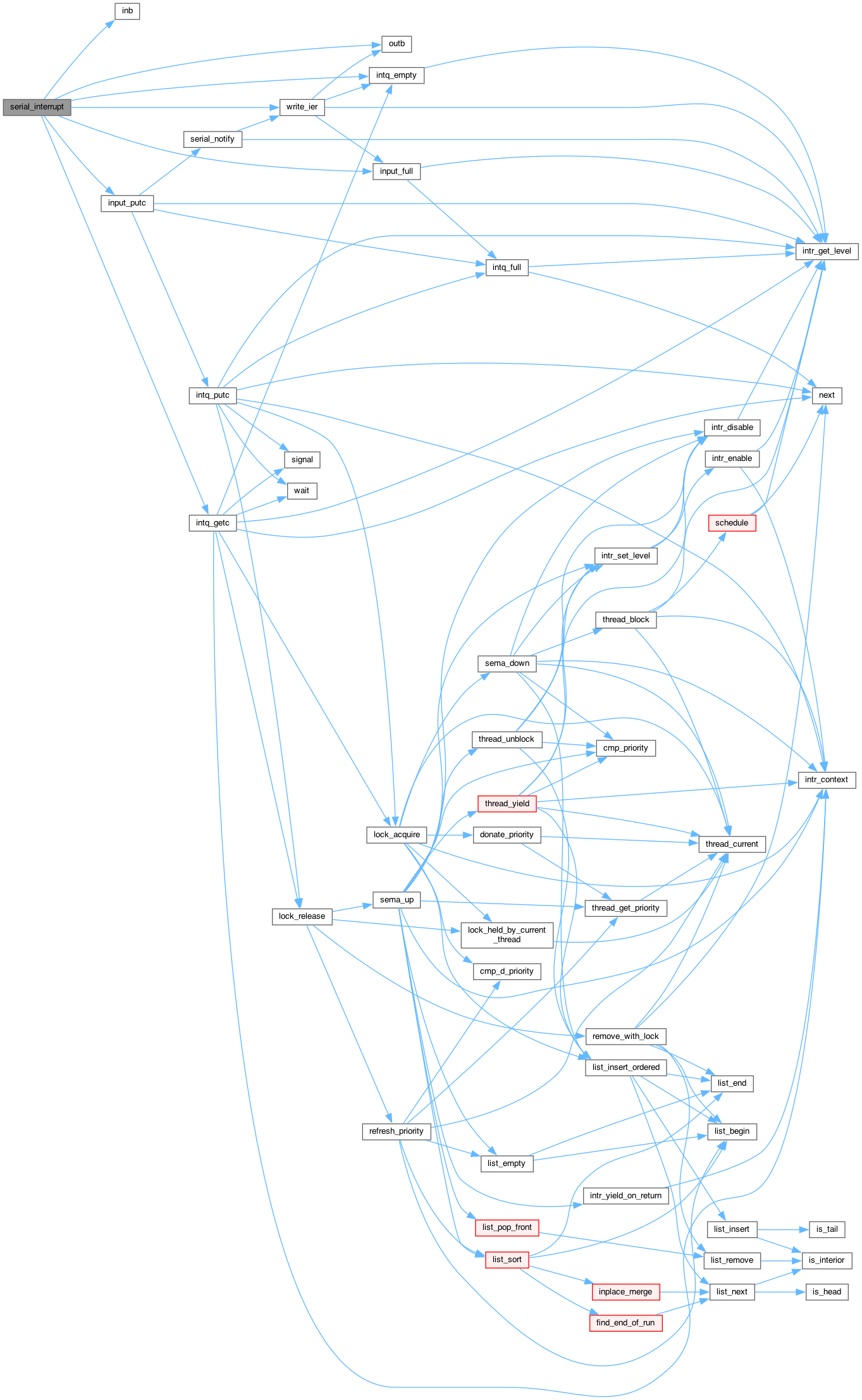

| static void | serial_interrupt (struct intr_frame *f UNUSED) |

Variables | |

| static enum { ... } | mode |

| static struct intq | txq |

| static intr_handler_func | serial_interrupt |

| #define IER_RECV 0x01 /* Interrupt when data received. */ |

| #define IER_REG (IO_BASE + 1) /* Interrupt Enable Reg.. */ |

| #define IER_XMIT 0x02 /* Interrupt when transmit finishes. */ |

| #define IO_BASE 0x3f8 |

| #define LCR_DLAB 0x80 /* Divisor Latch Access Bit (DLAB). */ |

| #define LCR_N81 0x03 /* No parity, 8 data bits, 1 stop bit. */ |

| #define LCR_REG (IO_BASE + 3) /* Line Control Register. */ |

| #define LS_REG (IO_BASE + 0) /* Divisor Latch (LSB). */ |

| #define LSR_DR 0x01 /* Data Ready: received data byte is in RBR. */ |

| #define LSR_THRE 0x20 /* THR Empty. */ |

| #define MCR_OUT2 0x08 /* Output line 2. */ |

| #define MCR_REG (IO_BASE + 4) /* MODEM Control Register. */ |

| #define MS_REG (IO_BASE + 1) /* Divisor Latch (MSB). */ |

| anonymous enum |

|

static |

|

static |

| void serial_flush | ( | void | ) |

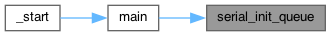

| void serial_init_queue | ( | void | ) |

|

static |

| void serial_notify | ( | void | ) |

| void serial_putc | ( | uint8_t | byte | ) |

|

static |

|

static |

| enum { ... } mode |

|

static |

|

static |